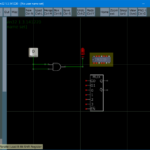

Logisimで組み合わせ回路(Combinational Logic)の比較回路(Comparator:コンパレータ)を学んでいきます。比較回路は、単純に2つの入力を比較して、その状態を出力します。

ひと桁の二進数の入力Aを考えると0か1です。

| 入力A |

|---|

| 0 |

| 1 |

比較するので、入力Bも考えると、これも0か1なので、入力Aと入力Bは、以下4通りの組み合わせがあります。

| 入力A | 入力B |

|---|---|

| 0 | 0 |

| 1 | 0 |

| 0 | 1 |

| 1 | 1 |

この表から、二進数で入力A、Bを比較すると、出力は値が同じ時、Aが小さい時、Aが大きい時の3パターンあることが分かります。AとBが両方とも0または1の時は、A-B=0と考えることもできます。

- A=Bの時は、0=0,1=1

- A<Bの時は、A0<B1

- A>Bの時は、A1>B0

これで出力のパターンが3つにまとまったので真理値表にします。

| 入力A | 入力B | A<B | A=B | A>B |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

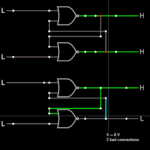

各出力の式を求める

A<Bの出力は、~AB

A=Bの出力は、~(~AB + A~B)

A>Bの出力は、A~B

つまり、A=Bは、A<BとA>Bの出力ピンをXNOR回路の入力とすればよいです。XNOR回路の求め方ですが、難しく考えるよりかは真理値表で、1001となってたらXNOR回路だ!と覚えてしまうのがよさそうです。

| A=B |

|---|

| 1 |

| 0 |

| 0 |

| 1 |

XNORを使わない解説が以下にあり分かりやすいです。

http://www.s-graphics.co.jp/nanoelectronics/kaitai/logicgate/4.htm

論理式、カルノー図、ベン図を学習すると、真理値表などを踏まえて回路図に落とせるようです。