JKフリップフロップを学んだことで二進数のカウンターを作れるようになりました。またLogisimにはHex Digit Displayという出力装置があるのでそれを繋げて16進数表記ができるようになりました。

2進数の4bitなので、0-15までのカウンターになります。今度はこれを7-Segment Displayで表示してみたいのですが、そのためにはエンコーダー、デコーダーを作ってみる必要があります。どうやって4桁の2進数を、2桁の10進数にして7セグメントに表示すればよいのでしょう。

プログラミング初心者向けチュートリアルやUnity5やC#の記事を書いています。

JKフリップフロップを学んだことで二進数のカウンターを作れるようになりました。またLogisimにはHex Digit Displayという出力装置があるのでそれを繋げて16進数表記ができるようになりました。

2進数の4bitなので、0-15までのカウンターになります。今度はこれを7-Segment Displayで表示してみたいのですが、そのためにはエンコーダー、デコーダーを作ってみる必要があります。どうやって4桁の2進数を、2桁の10進数にして7セグメントに表示すればよいのでしょう。

フリップフロップの仕組みを理解するためにDフリップフロップを作成しました。DはDelayの略で、クロック(CLK)の立ち上がりのタイミングでD入力の値をQ出力として保持します。NAND回路4つとNOT回路1つなので非常にシンプルです。

- Logisim cannot simulate subcircuits whose pins sometimes behave as inputs and sometimes behave as outputs. Components built using Java can have such pins, though: Within the built-in libraries, the Memory library’s RAM circuit contains a D pin that can act both as an input and as an output.

Logisimでは、組み合わせ回路はサブサーキットとして保存して、それをメインの回路図で使うことができます。例えばALUのサブサーキットを作成して、メインの回路図で汎用ロジックICのように部品として使えます。

だだし、入力と出力の振る舞いを持つピンがあるサブサーキットはシミュレートできないようです。ただしbuilt-inライブラリーとMemory Library’sのRAMサーキットはDピンを持っていますが動作するようです。

まだ「ときどき入力と出力の振る舞いを持つ」という意味が分かっていませんが、少なくとも、私がはじめに作成したDフリップフロップをさらに同じ回路につなげるようなことは問題ありませんでした。

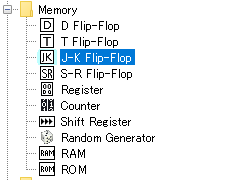

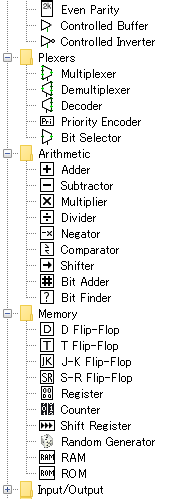

Logisimでは最初からFlipFlop回路が用意されているので、これを使って順序回路、フリップフロップの仕組みを学んでいきます。

まず、順序回路とは、出力をもう一度入力として使う回路のことです。これにより前の情報を保持することができます。レジスターやRAM、ROMはフリップフロップを大量に繋げることで実現しているようです。またカウンターは、1,2,3を前の数を踏まえて数え上げていくのでこれにもフリップフロップが必要になります。

Youtubeに、Logisimでカウンターを作る3分ぐらいの動画があったので、これからいろいろ調べていきます。

Logisimにある部品を使えばよいだけなので、フリップフロップ仕組みが分かっていなくても、すぐにカウンターを作る事ができました。

やっぱり、小さな回路のシミュレーションでも自分で作って動作するとうれしいですね。

最初はなぜこれでカウンターになるのかが分かりませんでしたが、ポイントはクロックです。

一番左のSマークがクロックで、このクロックの立ち上がり(電気が通る=1=薄い緑)で、一番左側のJKフリップフロップが動作します。クロックが薄い緑になるたびに、JKフリップフロップの出力Qが、薄い緑(=ON)または濃い緑(=OFF)になります。

出力Qを次のJKフリップフロップのクロック入力に繋げているのがポイントです。出力Qと出力~Qが交互になるという事は、入力信号に対してQは1/2でしかONにならなくなります。よって右隣りのJKフリップフロップは1/2の速度の動作になっていきます。

またJKフリップフロップは前の情報を保持しているので、2進数の各桁となり、バイナリーカウンターとなります。あとは、2進数を10進数に変換できればよさそうです!

上記でも4桁のカウンターが、0000,0001,0011,0100とカウントアップされているのが確認できます。

正論理のSRラッチを作成した際に、メニューの[Simulate]->[Reset Simulation]をすると、図の下のように、ワイヤーが赤になりおかしくなりましたが、とりあえず入力R押せば正常に動作できました。

入力のSet,Resetを1にしてみるとエラーが発生しました。SRフリップフロップはS=1,R=1の時は不定なのでこれは正しい挙動なのだとおもいます。

順序回路は、日本語のデジタル回路の入門サイトで学ぶことができるので問題ありませんが、Logisimで試してみたい場合は日本語のサンプルがないため、英語のサイトを調べるがあります。

Leanabout electronics には、順序回路(Sequential Logic)のSR Flip FlopsやJK Flip-flopsのLogisimのファイルがありダウンロードしてLogisimで試せます。

http://www.learnabout-electronics.org/Digital/dig54.php

http://www.learnabout-electronics.org/Digital/dig510extra.php#simlist

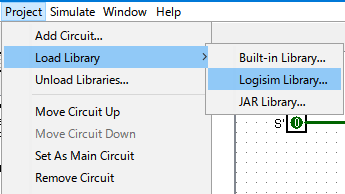

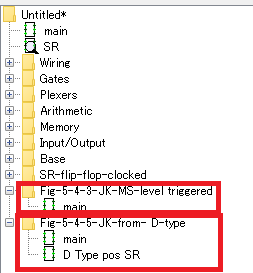

上記から、該当する.cricファイルを右クリックで適当な場所に保存します。メニューの[Project]->[Load Library]->[Logisim Library…]を選択すると、ダイアログが表示されるので保存した.cricファイルを選択するとロードされます。

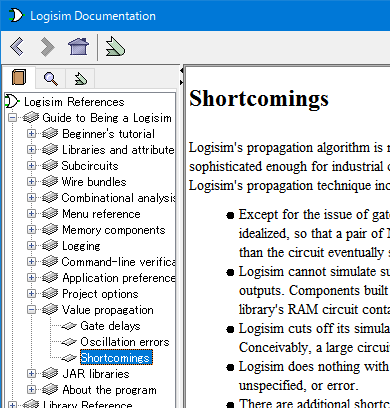

フリップフロップを調べると、出力された信号を入力信号に使うため、クロックの立ち上がりやタイミングが重要になってくることが分かってきます。メニューの[Help]でLogisim Documentationウィンドウを表示して、Logisim References->Value propagation->ShortcomingにLogisimの仕様が詳しく書かれています。

Logisimは教育目的では問題ないですが、産業用回路のデザインには十分でないと書かれています。ある程度割り切って使う必要があります。

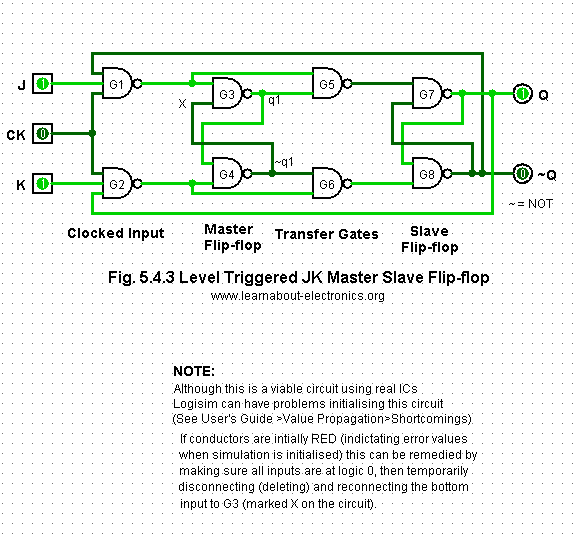

上記のように単純なJKフリップフロップはNAND回路から作る事ができないようです。ですが、いくつか条件がつきますが、JK Master Slave Flip-flopは作れるようです。

http://www.learnabout-electronics.org/Digital/dig510extra.php

Fig. 5.4.3 Level Triggered JK Master Slave Flip-flop

このサンプルのNOTEに書かれているように、SimulationをResetしたりすると、ワイヤーが赤くなって動かなくなります。その時は、一度NANDのG3につながっているXワイヤーを付け直せば動作します。ひとまずこれで、J=K=1の時に、Qと~Qで0,1を交互に繰り返す仕組みを再現できました。

よく見ると、NANDが8個で動作しているだけです。入力のクロックを入力JはKと同様に1bitの入力にして、自分で押しながら動作を追ってみればすぐに理解できそうです。

回路シミュレーターLogisimは、物理的なハードウェアではないので、トライアンドエラーがすぐにできて大変便利です。私でも、ここ数日でAND回路などからはじめてALUなども作れるようになりました。

せっかくなので、簡単なCPUの作り方を調べてみて、50ページぐらいの良い資料を見つけたので紹介です。

Gettysburg CollegeのCharles W.Kannさんがhttp://cupola.gettysburg.edu/oer/ でLogisimでのCPUの作り方「Implementing a One Address CPU in Logisim」を公開しています。

他にもIntroduction to MIPS Assembly Language ProgrammingやDigital Circuit Projectsなどの教材もあるようです。

本人のサイトhttp://chuckkann.com/ から、Logisimで完成したCPUのプロジェクトファイルをダウンロードすることが可能です。

http://chuckkann.com/joomlaMain/index.php/2016-05-09-22-19-35/one-address-cpu の下のほうに、Resources部分に、”OneAddressCPU.zip”リンクがあるのでここからダウンロードできます。

この教材の良いところは、実際に動作するプロジェクトファイルがある事です。Youtube動画などの場合は、真似すればLogisimの使い方が分かりますが、プロジェクトファイルが配布されていない場合も多く、何かトラブルが発生した場合に、先に進めなくなる場合は多々あります。

プロジェクトファイルがあると、自分で実装したものとの違いを比較してデバッグできるのでありがたいです。

昨日は、論理回路シミュレーターLogisimで、加減算器を作ったりALUを調べたりしていました。このような組み合わせ回路は、以前の動作に依存しないので問題ありませんが、フリップフロップのような順序回路の場合は、Logisimではうまくシミュレートしないようです。

ANDゲートを使って、JK Flip-Flopを作るなどではなく、用意されているJK FlipFlopを使って何かを作るという事は問題ないようです。

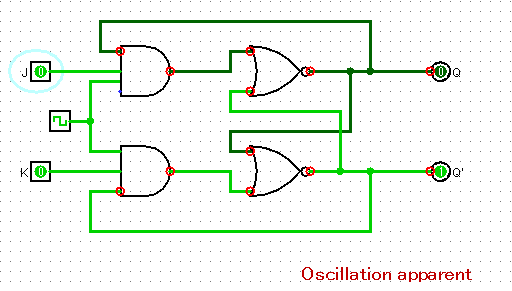

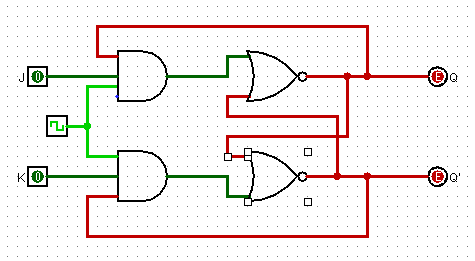

ちょうど、YoutubeにJK Flip Flopを作っている動画があったので試してみましたが、メニューからシミュレーションをリセットしたりすると以下のようになってしまいました。

http://www.cburch.com/logisim/docs/2.3.0/guide/opts/simulate.html

プロジェクトの設定で、Iterations Until OscillationやAdd Noise To Component Delaysなどがあるので、このようなパラメータで解決できるのかもしれませんが、まだわかりません。

その後調べていたら、以下を見つけました。ちょっと読んで試してみるとよさそうです。

http://electronics.stackexchange.com/questions/43168/what-is-wrong-with-my-d-flip-flop-toggle-switch