昨日は、論理回路シミュレーターLogisimで、加減算器を作ったりALUを調べたりしていました。このような組み合わせ回路は、以前の動作に依存しないので問題ありませんが、フリップフロップのような順序回路の場合は、Logisimではうまくシミュレートしないようです。

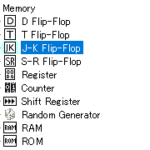

ANDゲートを使って、JK Flip-Flopを作るなどではなく、用意されているJK FlipFlopを使って何かを作るという事は問題ないようです。

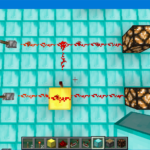

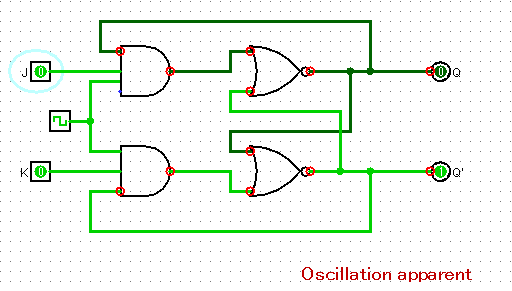

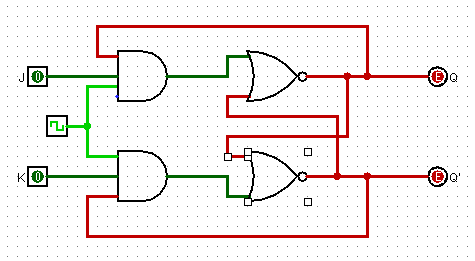

ちょうど、YoutubeにJK Flip Flopを作っている動画があったので試してみましたが、メニューからシミュレーションをリセットしたりすると以下のようになってしまいました。

http://www.cburch.com/logisim/docs/2.3.0/guide/opts/simulate.html

プロジェクトの設定で、Iterations Until OscillationやAdd Noise To Component Delaysなどがあるので、このようなパラメータで解決できるのかもしれませんが、まだわかりません。

その後調べていたら、以下を見つけました。ちょっと読んで試してみるとよさそうです。

http://electronics.stackexchange.com/questions/43168/what-is-wrong-with-my-d-flip-flop-toggle-switch